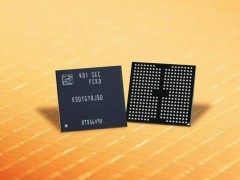

近期,韓國科技媒體ZDNet Korea報道了一則關于三星電子的最新動態。據悉,三星正在對其下一代DRAM內存技術——1c nm制程進行關鍵性的設計調整,旨在加速提升產品良率。

報道指出,三星原本為1c nm內存制定了極為嚴格的線寬標準,旨在通過增加存儲密度,提高單位晶圓的位元產出,從而在成本上確立對競爭對手的優勢。然而,這種極致的線寬要求也對工藝穩定性提出了前所未有的挑戰,導致良率方面遇到了一些困難。

據知情人士透露,為了克服這些挑戰,三星在2024年底對1c nm DRAM的設計方案進行了調整。具體來說,雖然核心電路的線寬保持不變,但外圍電路的線寬要求有所放寬。這一改變的目的,是為了盡快將1c nm內存的良率提升至足以支持大規模量產的水平。

這一調整對于三星來說至關重要,因為1c nm制程將被用于生產高性能的HBM4內存。同時,考慮到此前1b nm制程在良率方面遇到的一系列問題,1c nm制程能否順利進入量產階段,將直接影響到三星電子在未來幾年在DRAM領域的市場競爭力。

業界觀察家認為,三星此次的設計調整,是在面對技術挑戰時做出的靈活應對。通過放寬外圍電路的線寬要求,三星有望在不犧牲核心性能的前提下,提高生產效率和良率,從而確保1c nm制程DRAM內存的順利推出。